UP dated 2017.07.13 Up2018.03.21 Up2018.05.06(PICプログラム修正)

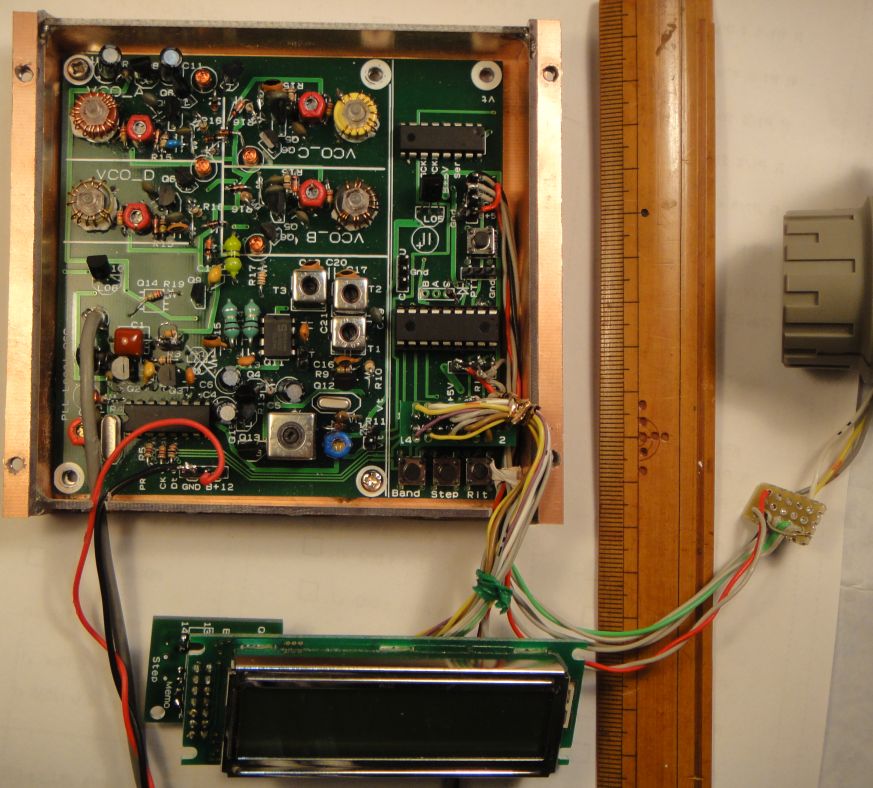

PLL ICは、左下端の東芝TC9256P。

PLL 制御は、PIC16F819(LCD下に隠れている)。

4つの

VCO_A(15-21MHz),

VCO_B(21-27.4MHz),

VCO_C(27.4-34.4MHz),

VCO_D(34.4-42MHz) により

HF9バンド(3.5-28MHz: UpHet.)

及び50MHz(Lower Het.) をカバーしている。

VCOコイルは、アミドンコアT37-#2,or #6にUEWφ0.4を巻いた。外部の影響を受けやすいかもしれないが、10kボビンに巻いたコイルよりもQは高い感じで信号純度は高い。

PLL基板調整の際は、この基板にLCD16x2を直接差し込みます(上写真)。

リグに組込むときは、そのソケット7Px2経由で 前面パネル設置LCDとします(左の写真)

中央下の10Kボビンが、VXO(62.820kHz-62.810kHz)用コイル

その上側の 7Kボビン x3個は、62.8MHz BPFコイル。

右側のICは、下がトランンシーバを制御するPIC16F819(DIPソケットで抜き差し可能)で、

上が74HC595P(VXOを10kHz動かす電圧0-5Vを発生)。

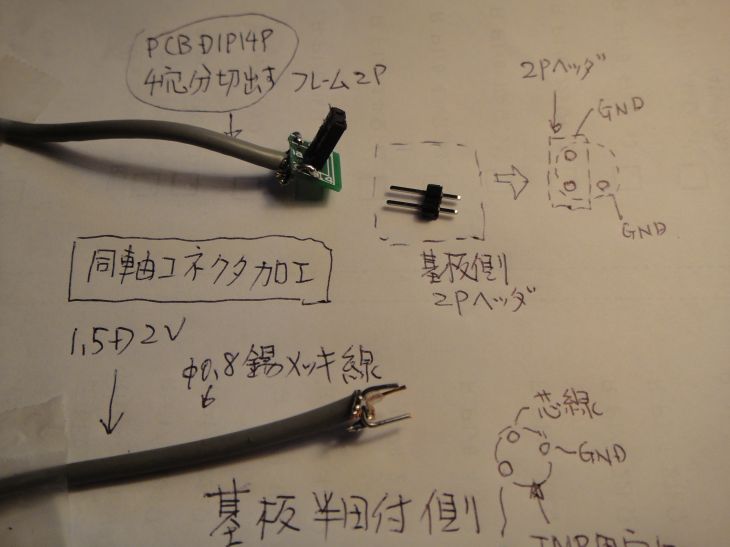

VCOのLo出力は、大宏TMPコネクタで取り出すような基板パターン穴としているが、最近は、このTMPが入手できない。

その代替品として、左写真のように、ピンヘッダ2P と2Pソケットで Plug and Socketを製作している。 1.5D2Vケーブルの反対側は、基板に直接半田付けし、片側のみこのPlug and Socketを使う。

PLL VCO基板の回路図は、下図のとおり。

PLL IC、TC9256Pの比較周波数Frは、10kHzステップで 10kHz幅を連続可変補間するVXO(62.820kHz-62.810kHz)とVCO周波数との加算周波数(78-105MHz)を PLLにフィードバックし、制御している。

VXO(62.820kHz-62.810kHz)は、原発振周波数20.945MHzのXtalを 20.940-20.9367MHzで発振させ、2SC1923のコレクタより、その3逓倍62.8MHzを取り出している。

4つの 各VCOは、回路図に記載されている周波数範囲を分担している。周波数によりTC9256PのPin6,7,8により自動的にVCOを切り替えている。

それぞれのVCOの最大、最小周波数比は、fmax/fmin≒1.4であるが、PLLとしては、広すぎる感じで、適切なPLL-LPF゚定数を決めることは難しい。、試作品では、全バンドともにSSB運用には差し支えなく、SSBを聞く範囲では気にならないが、 ジェネカバ受信機で、VCO発振周波数と直接ビートをとると、VCO出力成分に、少しFM留分(Jitterジッター)が残っているようで、ビブラートを感じる。

Q11NE602から出力される加算周波数(78-105MHz)の信号レベルは、50-100mVで、当初は2SC1906のアンプで増幅しようとしたが、TC9256Pの入力感度は高く、30mVあれば、十分にカウントするので、2SC1906アンプは、省略した。

PLL制御は、PIC16F819を使っている。TC9256Pの制御、VXO可変用電圧(0V-3.88Vボルト、200step)用74HC595P、9band LPF切替用74HC595P(RF Converter基板の実装)の制御も行っている。 このLPF切替用74HC595は、RF Converter基板に実装されるので、その制御信号は5x2Pソケットで結線される。

PLL制御のブロック系統は、左図のとおり。

クロック周波数は、8MHzでTC9256P内部で800分周し、比較周波数は、Fr=10kHz。各VCOとVXO(62,810kHz)との加算周波数を、TC9256Pに入力し、それを ロータリエンコーダで設定したNrで、分周した信号 Fvを、基準のFr=10kHzとの比較で、VCO制御電圧を上げたり下げたりする。

比較(ステップ)周波数は、10kHzなので、その間を補間するのに、VXO(62,810-62,820kHz)を10kHz、200stepで動かしている。

TC9256Pの Pin15/DO1の動作は、

1) Fv>Frであれば、その周波数偏差に比例した時間長さの プラスパルス(+5V)を発信する。

2) Fv<Frであれば、その周波数偏差に比例した時間長さの 接地パルス(+0V)を発信する。

3) Fv=Frであれば、Pin15は、トライステート・ハイインピーダンスとなり、Q2_2SK246には、何の影響も与えない。

1)のときは、VCO制御電圧を下げ、2)のときは、VCO制御電圧を上げ、3)のときは、C1マイラコンに蓄電している電荷で、Q2_2SK246のゲート電圧を一定に保ち続ける。2SK246のゲートインピーダンスは、非常に高く、データシートから推定すると、30,000MΩというレベルで、周辺のPCBの漏れ、TC9256Pのパッケージの漏れ等を考慮しても1,000MΩは、確保できていると思われる。 するとC1マイラコンとの時定数は、τ=1000secとなり、2SK246のゲート電圧は、そう短時間では変化しない。ということは、VCOの発振周波数は、一定に保持されるということに他ならない。

PLLの調整の勘どころは、

A) TC9259P_Pin15〜2SK246ゲート間の高インピーダンス箇所への ノイズ混入を抑える。

例として、60W半田ごてのAC100Vケーブルを 10mmの距離に近づけると、VCO信号に50Hzハム音が混入するのがわかる。 また、30W半田ごて、これは、サイリスタ制御による過加熱防止装置を取り付けているが、このACケーブルを 30mm程度に近づけると、PLLは、プルプルとロック外れを起こす。

B) 2SK246のソース抵抗での降下電圧を 2SC1815のベース電流が流れ出す寸前の電圧(0.47V;TRによりバラツキあり)とする。

2SK246-YのIdss特性に依存するが、試作機1台目では、ソース抵抗=870Ω(1k+6.8k) であった。3台目では、1470Ωであった。

C) PLLの LPFの適正化

R1=1.2k、R2=3.2k、C1=1uFからなる LPFの時定数を適正に調整します。これらの値の計算は、添付XLSを参照ください。

◇ダウンロード PLL_LPFの時定数xlsファイル

PLL VCOの改善、調整のHintを ◇「KP6トランシーバの改善点、追加データ、Hintのページ」の Hint4 および ◇PLL改善説明.pdfに追加したので、それも参照ください/2018.03.21追加。

プログラムソースは、マウス右クリックで「対象をファイルに保存」を選んで、ダウンロード。

PIC16F819用プログラム

◇ダウンロード KP6T1.hexのzipファイル

Memory起動時の動作不良を修正。 KP6T ⇒ KP6T1 //2018.05.06

このプログラムでは、

・Bandボタンを押すたびに、7M→10M→14M→18M→21M→24M→28M→50→3.5M→そして7Mへ循環する。

・Stepボタンを押すとロータリーエンコーダーのSTEPが、 50Hzと 10kHzが切り替わる。

・Ritボタンを押すと RIT ON/OFFが切り替わる。RIT範囲は、±6.4kHz

・Memoボタンを押すと、そのときの周波数Band、周波数をEEPROMメモリーにSAVEする。次回電源投入時にメモリーで起動する。

・Ritボタン(Rb.7)を押しながら電源投入すると VXO(62.820kHz-62.810kHz)調整モードとなるので、0-199(HC595P R-2Rの電圧;0V-3.88V)の200stepで所定の周波数範囲となるように調整する。

"ひとつ前に戻る"には、ブラウザの「戻る」で戻ってください。

◇ホームページ インデックスへ戻る