UP dated 2020.08.11

基板サイズは、100x50mm。

PLL局発がうまく動作すると、確認のため実際にSSBを受信してみたくなります。

そのための 実験用 TRX基板を (K13)に付属しました。 受信系だけとする、送信系だけとする、あるいは、若干の付加回路を追加して、250mW SSB_CWトランシーバーとすることも可能です。

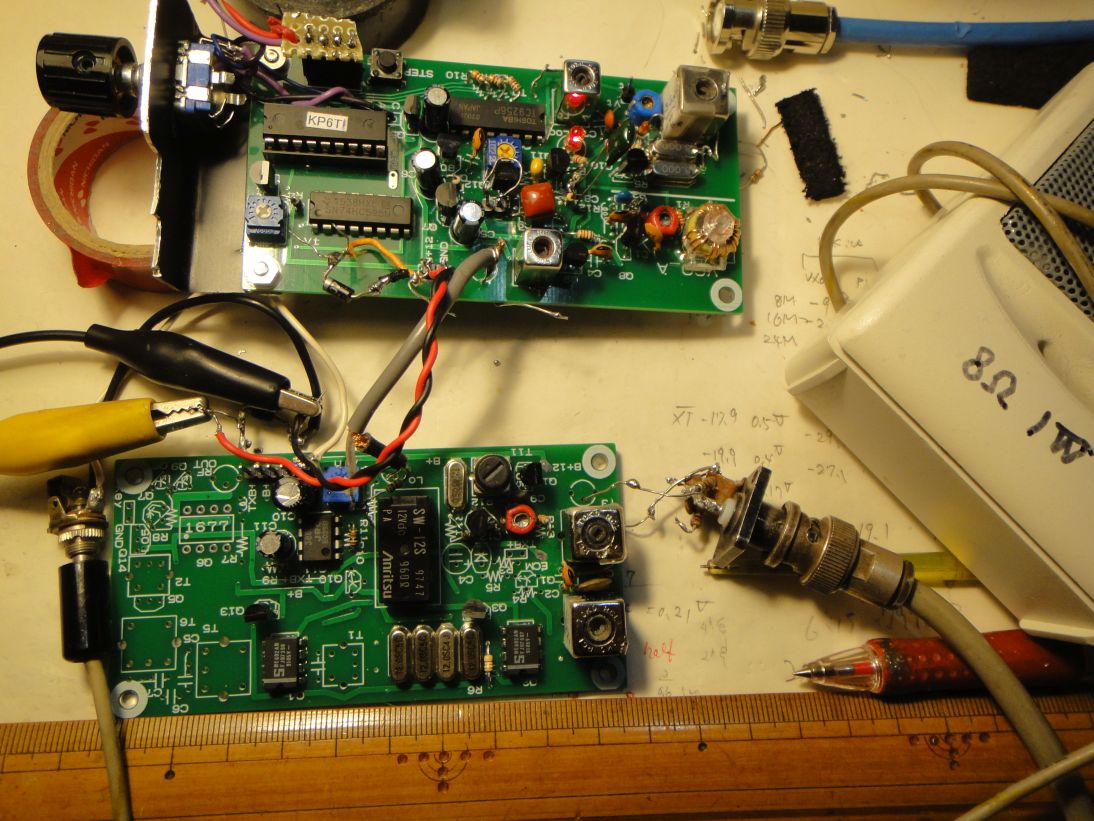

左側のこの試作例では

若干の付加回路を 基板上空中配線で追加して、250mW SSB_CWトランシーバー

としています。

送信系統は、

Mic →DBM NE602 →12MHz XF →Mix NE602 →7M BPF →RF Amp J310 + RD00HVS1(500mW)

右側の10Kコイルx2個が受信用7MHz FCZコイル。左下の10kx2個が送信用。

これは、RX系統のみ部品を取り付けて、7MHzを受信している状態です。

上が PLL局発基板で 下がTRX基板です。

高一中二 ではなく、高ゼロ中ゼロ NE602-NE602-LM386受信機ですが、快適に受信できます。 CWであれば、S1(-120dBm)の信号も聞こえます。

AGCはないので、強い信号は強く、弱い信号は、それなりに弱く聞こえます。 ANTを外すと、壊れているかのごとくに、静かに黙り込みます。

RXとしてのブロックダイアグラムは、左図のとおり。

左側のNE602には、PLLからの局発信号を、右側のNE602には、プロダクト検波のキャリア(12MHz)を注入する。

各ポイントの ゲイン、信号レベルの計算値を併記しているが、S1(-120dBm)の信号受信の感度がある。

このままでも 7MHz帯では十分実用的であるが、できれば、IF段、XFの後に、RX時専用の +20dB程度のアンプを入れたい。

TXとしてのブロックダイアグラムは、左図のとおり。

受信の時とは逆に、左側のNE602には、SSBのキャリア(12MHz)を注入、右側のNE602には、PLLからの局発信号を注入する。

出力250mWと記載しているが、7MHzバンドの試作機では、500mWの出力を確認した。

このままでも 右側のNE602への IF(12MHz)信号レベルは高く、飽和寸前なので、右のNE602の直前にアンプをいれることはできない。

RX時はアンプがほしいが、TX時には入れることができない、という系統になる。

1) 12MHzキャリア周波数の調整。

LSBキャリアポイントは、11.999.2kHz(上側ヘテロダインでは、USB)

USBキャリアポイントは、11.996.2kHz(上側ヘテロダインでは、LSB)

送信時 CWキャリアポイントは、11.997.0kHz

SSB専用機とする場合は、キャリア周波数は、常に、11.999.2kHz、または11.996.2kHz

固定なので、T11コア調整により、この周波数に合わせる。

T11コアの下流の1SV231へのTXB+電源供給は不要なので、そのパターンはカットする。(あるいは、1SV231を取り付けない)

高い周波数の11.999.2kHzの場合は、T11は切り離し、2SC1815のベースの左図では黒点のポイントに、20pF程度のTCを接続し、周波数合わせをする。

CW送信機では;受信時11.996.2kHz、送信時11.997.0kHzの周波数シフトが必要なので、1SV231への荷電(+12V)あり、なし(GND)、で、この700Hzシフトを行う。

1SV231の容量は 8pF(+12V)〜 70pF(0V)の変化をするので、この変化で 700Hzシフトするように、TC2 20pFを調整する。20pFで不足する場合は、並列に10pFセラコンを追加する。

RF終段 RD00HVS1 単段での入出力特性は、左表のとおり。

出力段のコアに、小さく低インダクタンスの FB101x2個を使ったことから、低域(3.5M)よりも 高域(50MHz)で出力が大きく得られる。

それにしても、3.5M〜50Mの広範囲に亘り、一定の出力を出せる このRDシリーズのFETは素晴らしい。

出力段のコアの設計について

ちょっと特殊な バイファイラ巻きとしている。B+でパスコン接地の端子を コールドエンドとし、RD00のドレインを ホットエンドとすると、その途中に50Ω出力端子タップがある。

このコアは、コールドエンド側より、3t:5t となり、インピーダンス比は、タップ比の二乗なので、9:25=50Ω:139Ω となる。Zo=139Ω

このとき、RD00HVS1で出せる 計算上の最大出力Poは、

Po=(Vdd-1)^2 /(2x Zo) ∵Vdd=B+電圧、Zo=ドレインインピーダンス=139Ω Vddから引いている1は、FET On抵抗による電圧降下分(損失分 1V程度)

∴Po=(13.5-1)^2 /(2x 139) =0.562 W

これで RD00HVS1の持てる能力の最大パワーを引き出せる。

その他の基板の詳細は、以下のページへ。

このPLL KITの詳細 ◇(K13) PLL 局発 と実験TRX基板のページへ

本TRX基板出力250mWを4Wにする ◇(OPTION-12) バッタもんリニアアンプのページへ

コンパクトなタッチエレキー ◇タッチエレキーのページへ

"ひとつ前に戻る"には、ブラウザの「戻る」で戻ってください。

◇ホームページ インデックスへ戻る